# **FDK REFERENCE MANUAL AGILENT ACQIRIS ANALYZERS / STREAMER ANALYZERS**

**Models covered:**

U1080A AC240/AC210 SC240/SC210

#### **Manual Part Number**

#### U1092-90010

#### Edition

C-RevA, November 2007

The information in this document is subject to change without notice and may not be construed in any way as a commitment by Agilent Technologies, Inc. While Agilent makes every effort to ensure the accuracy and contents of the document it assumes no responsibility for any errors that may appear.

All software described in the document is furnished under license. The software may only be used and copied in accordance with the terms of license. Instrumentation firmware is thoroughly tested and thought to be functional but it is supplied "as is" with no warranty for specified performance. No responsibility is assumed for the use or the reliability of software, firmware or any equipment that is not supplied by Agilent or its affiliated companies.

You can download the latest version of this manual from http://www.agilent.com/ by clicking on Manuals in the Technical Support section and then entering a model number. You can also visit our web site at

http://www.agilent.com/find/acqiris. At Agilent we appreciate and encourage customer input. If you have a suggestion related to the content of this manual or the presentation of information, please contact your local Agilent Acqiris product line representative or the dedicated Agilent Acqiris Technical Support (ACQIRIS\_SUPPORT@agilent.com).

# **Acqiris Product Line Information**

USA (845) 782-6544

Asia - Pacific 61 3 9210 2890

Europe 41 (22) 884 32 90

© Copyright Agilent 2007

# CONTENTS

| 1. | INT            | RODUCTION                                                     | 10 |

|----|----------------|---------------------------------------------------------------|----|

|    | 1.1            | Message to the User                                           | 10 |

|    | 1.2            | Using this Manual                                             | 10 |

|    | 1.3            | Conventions Used in This Manual:                              | 11 |

|    | 1.4            | Warning Regarding Medical Use                                 | 11 |

|    | 1.5            | Warranty                                                      | 11 |

|    | 1.6            | Warranty and Repair Return Procedure, Assistance, and Support | 11 |

|    | 1.7            | System Requirements                                           | 11 |

| 2. | INS            | TALLATION                                                     | 12 |

|    | 2.1            | Preliminary Remarks                                           |    |

|    | 2.2            | Installation Types                                            |    |

|    | 2.3            | FDK Installation                                              |    |

|    | 2.4            | Checking Your Installation                                    |    |

|    | 2.5            | Recommendations on Beginning a New Design                     |    |

|    |                | COVERVIEW                                                     |    |

|    | 3.1            | The FPGA Cores                                                |    |

|    | 3.1<br>3.2     | Base Designs                                                  |    |

|    |                |                                                               |    |

|    | 3.3<br>3.4     | Reference Designs                                             |    |

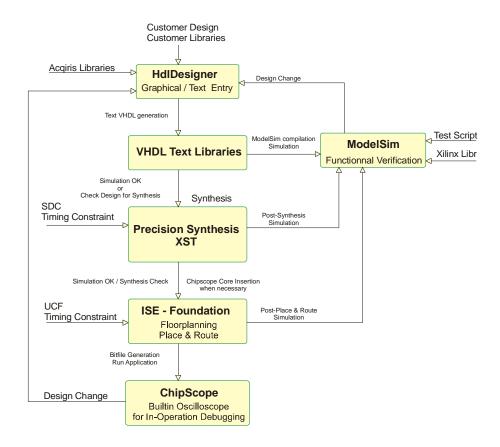

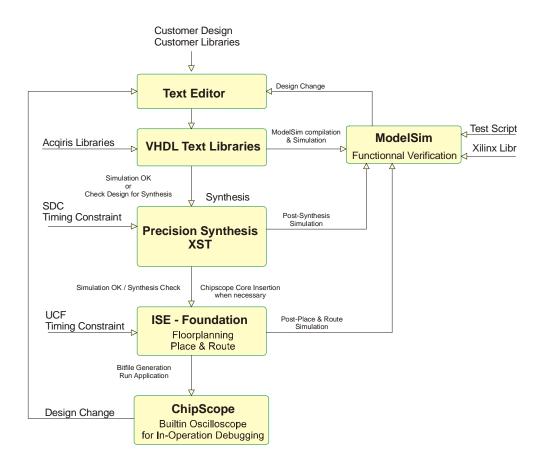

|    |                | The FPGA Design Tools                                         |    |

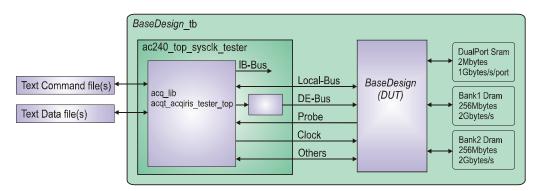

|    | 3.5            | The Acquiris Test Bench                                       |    |

|    | 3.6            | The .bit File Header                                          |    |

|    | 3.7            | Overview of the FPGA Core Structure                           |    |

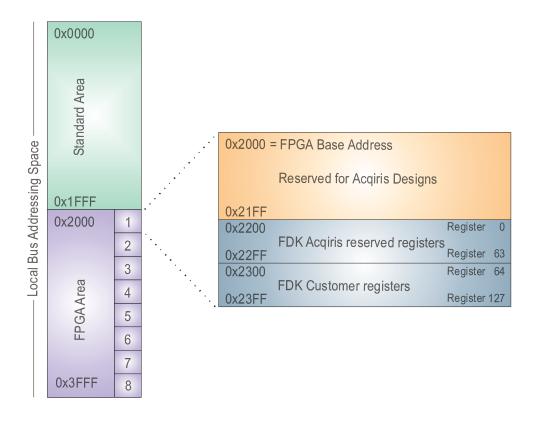

|    | 3.8            | Accessing Registers and Memories                              |    |

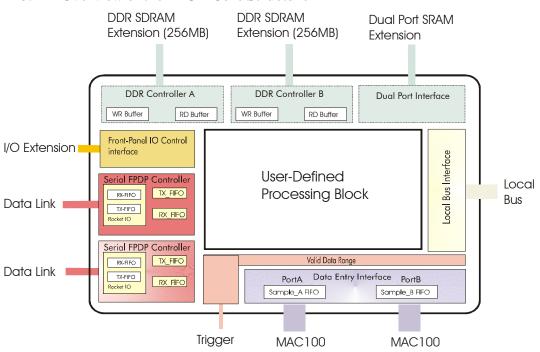

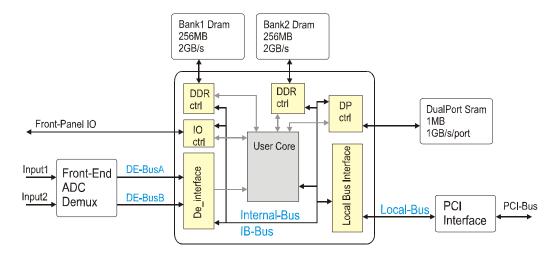

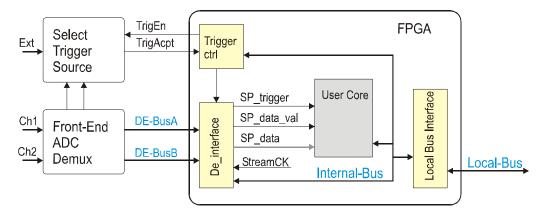

| 4. |                | ERVIEW OF THE DATA PROCESSING UNIT                            |    |

|    | 4.1            | Digitizer                                                     |    |

|    | 4.2            | Data Processing Unit (DPU)                                    |    |

|    | 4.2.           |                                                               |    |

|    | 4.2.2          |                                                               |    |

|    | 4.3            | Understanding DMA Transfers                                   |    |

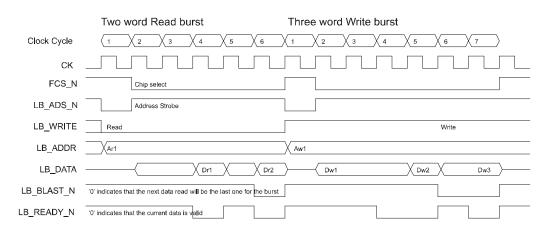

|    | 4.4            | Local Bus                                                     |    |

|    | 4.4.           |                                                               |    |

|    | 4.4.2          |                                                               |    |

|    | 4.4.3          | 200 a 2 de 1 ming                                             |    |

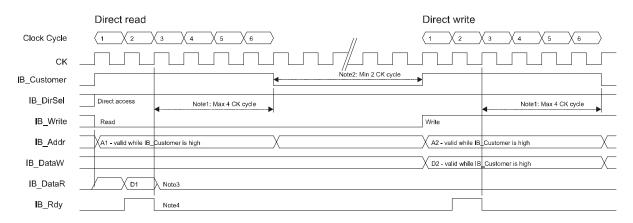

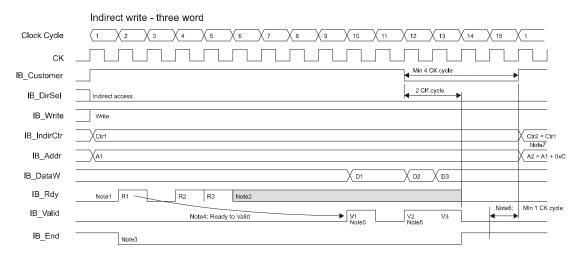

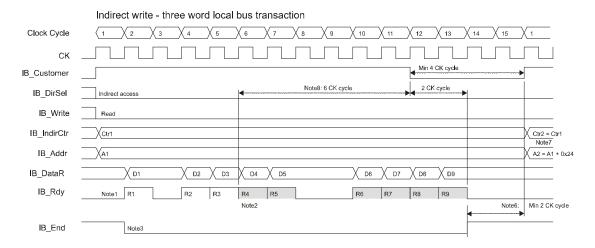

|    | 4.5            | Internal Bus                                                  |    |

|    | 4.5.           |                                                               |    |

|    | 4.5.2          |                                                               |    |

|    | 4.5.3<br>4.5.4 | 6                                                             |    |

|    | 4.5.4          |                                                               |    |

|    | 4.5.           |                                                               |    |

|    | 4.5.           |                                                               |    |

|    | 4.5.8          |                                                               |    |

| 5. |                | SE DESIGN                                                     |    |

|    | 5.1            | Multiple Base Designs                                         |    |

|    | 5.2            | Bitfile name for the Base Design                              |    |

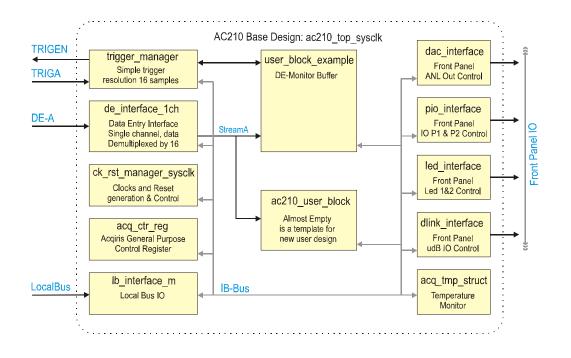

|    | 5.2<br>5.3     | Overview of the Base Design                                   |    |

|    | 5.5<br>5.3.    | e e                                                           |    |

|    | 5.3.           | 0                                                             |    |

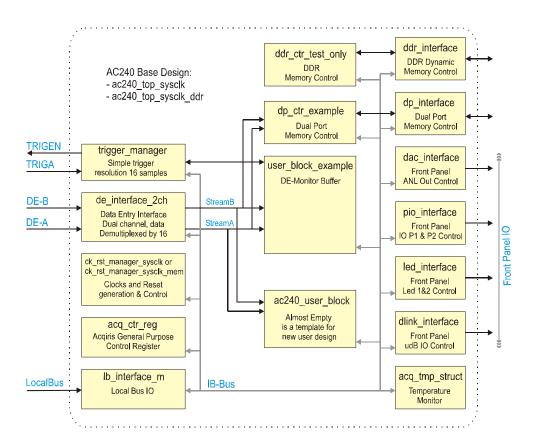

|    | 5.3<br>5.4     | AC240 Base Design                                             |    |

|    | 5.4<br>5.4.    | -                                                             |    |

|    | 5.4.<br>5.4.   |                                                               |    |

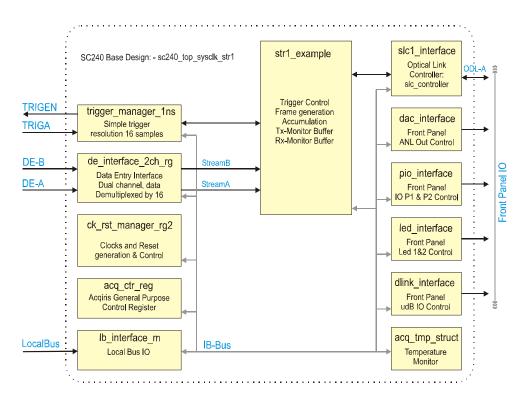

|    | 5.4.<br>5.5    | SC240 Base Design                                             |    |

|    | 5.5<br>5.5.1   |                                                               |    |

|    | 5.5.           | Areineeture or uie base Sucanning Fillinwale                  | 20 |

|   | 5.5.2 | Trigger Positioning Resolution versus Sampling Rate | 29 |

|---|-------|-----------------------------------------------------|----|

|   | 5.5.3 | Trigger Time Stamp                                  | 30 |

|   | 5.5.4 | Front Panel LED Status                              | 30 |

| 4 |       | List of Cores Instantiated in Base Designs          |    |

| 4 | 5.7   | Register List in Base Designs                       | 31 |

| 4 | 5.8   | Indirect Addressing in AC2x0 Base Designs           | 33 |

| 4 | 5.9   | Indirect Addressing in SC2x0 Base Designs           | 33 |

| 4 | 5.10  | Simulation                                          | 34 |

| 4 |       | Constraints                                         |    |

|   |       | Interrupt Control                                   |    |

|   |       | Resource Utilization                                |    |

|   |       | Version History                                     |    |

|   |       |                                                     |    |

|   |       | CORE LIBRARY                                        |    |

|   |       | Index of Available Cores                            |    |

| ( |       | Base Clock Manager                                  |    |

|   | 6.2.1 |                                                     |    |

|   | 6.2.2 | F                                                   |    |

|   | 6.2.3 |                                                     |    |

|   | 6.2.4 |                                                     |    |

|   | 6.2.5 |                                                     |    |

|   | 6.2.6 |                                                     |    |

|   | 6.2.7 |                                                     |    |

|   | 6.2.8 |                                                     |    |

| ( |       | Memory Option Clock Manager                         |    |

|   | 6.3.1 | · · · · · · · · · · · · · · · · · · ·               |    |

|   | 6.3.2 | Ī                                                   |    |

|   | 6.3.3 |                                                     |    |

|   | 6.3.4 |                                                     |    |

|   | 6.3.5 |                                                     |    |

|   | 6.3.6 |                                                     |    |

|   | 6.3.7 |                                                     |    |

|   | 6.3.8 | · · · · · · · · · · · · · · · · · · ·               |    |

| 6 | 5.4   | Streamer Clock Manager                              |    |

|   | 6.4.1 | <b>r r</b>                                          |    |

|   | 6.4.2 |                                                     |    |

|   | 6.4.3 |                                                     |    |

|   | 6.4.4 |                                                     |    |

|   | 6.4.5 |                                                     |    |

|   | 6.4.6 |                                                     |    |

|   | 6.4.7 |                                                     |    |

| ( |       | User Block Skeleton                                 |    |

|   | 6.5.1 | Ī                                                   |    |

|   | 6.5.2 | ·                                                   |    |

| 6 |       | User Block Example                                  |    |

|   | 6.6.1 |                                                     |    |

|   | 6.6.2 | F                                                   |    |

|   | 6.6.3 | Registers                                           | 55 |

|   | 6.0   | 5.3.1 User Control Register                         | 55 |

|   |       | 5.3.2 User Status Register                          |    |

|   | 6.6.4 |                                                     |    |

|   |       | 5.4.1 IN-Buffer                                     |    |

|   | 6.6.5 |                                                     |    |

|   | 6.6.6 |                                                     |    |

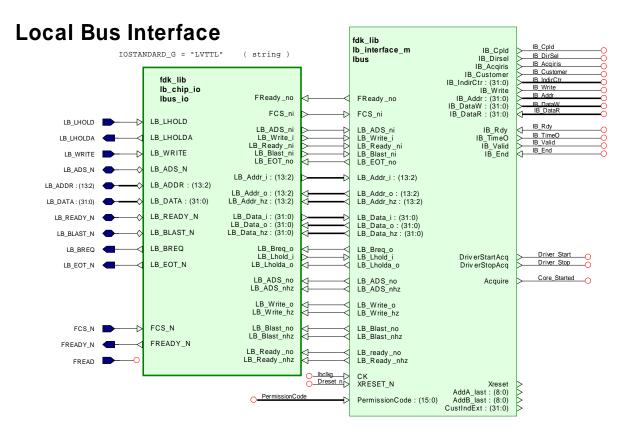

| ( | 5.7   | Local Bus Interface                                 |    |

|   | 6.7.1 | Functional Description                              | 57 |

|   | 6.7.2 | Instantiation                                       | 57 |

|   | 6.7.3 | Port Description                                    | 58 |

| 6.7.4     | Access Time Out                                 | .60  |

|-----------|-------------------------------------------------|------|

| 6.7.5     | Protection of Firmware Code                     | .60  |

| 6.7.6     | Registers                                       | .60  |

| 6.7.6.1   | Overview                                        | . 60 |

| 6.7.6.2   | Indirect Access Port                            | . 60 |

| 6.7.6.3   | Indirect Address Register                       | . 60 |

| 6.7.6.4   | Buffer Identifier Register                      | . 61 |

| 6.7.6.5   | Code Protection Register                        | . 61 |

| 6.7.6.6   | Direct Access Block Register                    | . 61 |

| 6.7.7     | Constraints                                     |      |

| 6.7.8     | Resource Utilization                            |      |

| 6.7.9     | Version History                                 |      |

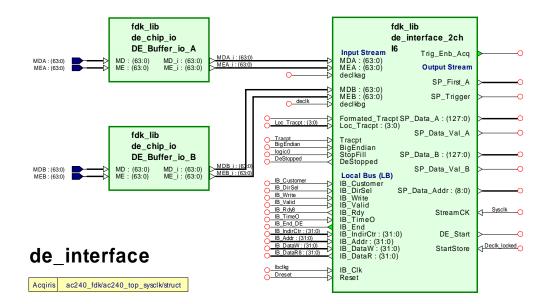

| 6.8 DE    | Interface for 1 and 2 Channels                  | .63  |

| 6.8.1     | Functional Description                          | .63  |

| 6.8.2     | Instantiation                                   | .63  |

| 6.8.3     | Port Description                                | .64  |

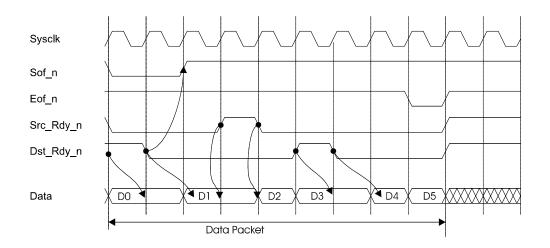

| 6.8.4     | Output Stream Bus                               | .65  |

| 6.8.4.1   | Data Source and Ordering                        | . 66 |

| 6.8.4.2   | ADC Code Correspondence                         | . 66 |

| 6.8.5     | Registers                                       | .66  |

| 6.8.5.1   | DEControl Register                              | . 66 |

| 6.8.5.2   | DE_Buffer Operating Mode                        | . 68 |

| 6.8.6     | Accessing the DE-Buffer                         | .68  |

| 6.8.6.1   | DE-Buffer                                       | . 68 |

| 6.8.7     | Constraints                                     | .68  |

| 6.8.8     | Resource Utilization                            |      |

| 6.8.9     | Version History                                 |      |

| 6.9 DE 1  | Interface for SC240 and High Resolution Trigger | .70  |

| 6.9.1     | Instantiation                                   |      |

| 6.9.2     | Port Description                                | .70  |

| 6.9.3     | Version History                                 | .71  |

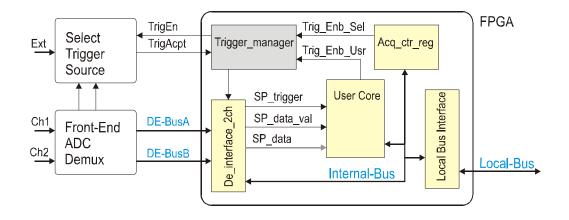

| 6.10 Trig | ger Manager                                     | .72  |

| 6.10.1    | Functional Description                          | .72  |

| 6.10.2    | Port Description                                | .72  |

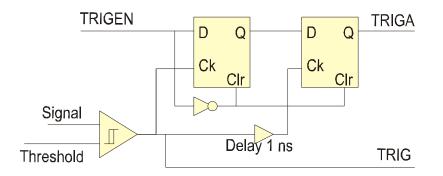

| 6.10.3    | Trigger and Trigger Accept Circuit              | .73  |

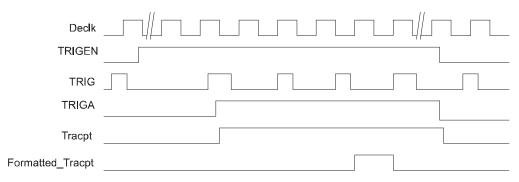

| 6.10.4    | Trigger Control Timing Diagram                  | .73  |

| 6.10.5    | Constraints                                     | .73  |

| 6.10.6    | Resource Utilization                            | .73  |

| 6.10.7    | Version History                                 | .74  |

| 6.11 High | n Resolution Trigger Manager                    | .75  |

| 6.11.1    | Functional Description                          | .75  |

| 6.11.2    | Port Description                                | .75  |

| 6.11.3    | Registers                                       | .76  |

| 6.11.3.   | 1 Trigger Control Register                      | . 76 |

| 6.11.3.2  | 2 Trigger Status Lo                             | . 77 |

| 6.11.3.   | 3 Trigger Status Hi                             | . 77 |

| 6.11.3.4  | 4 Trigger Delay                                 | . 78 |

| 6.11.4    | Constraints                                     | .78  |

| 6.11.5    | Resource Utilization                            | .78  |

| 6.11.6    | Version History                                 | .78  |

| 6.12 Acq  | iris Register                                   | .79  |

| 6.12.1    | Functional Description                          | .79  |

| 6.12.2    | Port Description                                |      |

| 6.12.3    | Registers                                       |      |

| 6.12.3.   |                                                 |      |

| 6.12.3.2  |                                                 |      |

| 6.12.3.   |                                                 |      |

| 6.12.4    | Constraints                                     |      |

| 6.12.5           | Resource Utilization                     | 81 |

|------------------|------------------------------------------|----|

| 6.12.6           | Version History                          | 81 |

| 6.13 LEI         | ) Interface                              | 82 |

| 6.13.1           | Functional Description                   | 82 |

| 6.13.2           | Port Description                         | 82 |

| 6.13.3           | Detailed Description                     |    |

| 6.13.4           | Register                                 | 83 |

| 6.13.4           | 1 LED Control                            | 83 |

| 6.13.5           | Constraints                              |    |

| 6.13.6           | Resource Utilization                     |    |

| 6.13.7           | Version History                          |    |

| 6.14 PIC         | Interface                                |    |

| 6.14.1           | Functional Description                   |    |

| 6.14.2           | Port Description                         |    |

| 6.14.3           | Detailed Description                     |    |

| 6.14.4           | Register                                 |    |

| 6.14.4           |                                          |    |

| 6.14.5           | Instantiation                            |    |

| 6.14.6           | Constraints                              |    |

| 6.14.7           | Resource Utilization                     |    |

| 6.14.8           | Version History                          |    |

|                  | perature Interface                       |    |

| 6.15.1           | Functional Description                   |    |

| 6.15.2           | Port Description                         |    |

| 6.15.3           | Detailed Description                     |    |

| 6.15.4           | Register                                 |    |

| 6.15.4           | 1                                        |    |

| 6.15.5           | Constraints                              |    |

| 6.15.6           | Resource Utilization                     |    |

| 6.15.7           | Version History                          |    |

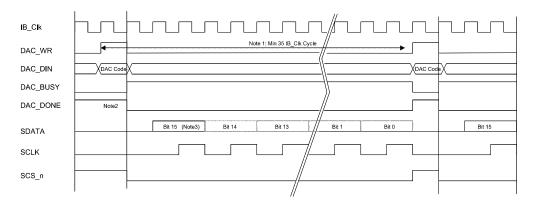

|                  | C Interface                              |    |

| 6.16.1           | Functional Description                   |    |

| 6.16.2           | Port Description                         |    |

| 6.16.3           | Detailed Description                     |    |

| 6.16.4           | Register                                 |    |

| 6.16.4           |                                          |    |

| 6.16.5           | Constraints                              |    |

| 6.16.6<br>6.16.7 | Resource Utilization                     |    |

|                  | Version History                          |    |

|                  | ık Interface<br>Functional Description   |    |

| 6.17.1<br>6.17.2 | 1                                        |    |

| 6.17.2           | Port Description<br>Detailed Description |    |

| 6.17.3<br>6.17.4 | Registers                                |    |

|                  | -                                        |    |

| 6.17.4           | _                                        |    |

| 6.17.4<br>6.17.4 | - 6                                      |    |

| 6.17.4           | 3 DLink_Din Register<br>Instantiation    |    |

| 6.17.6           | Constraints                              |    |

| 6.17.7           | Resource Utilization                     |    |

| 6.17.8           | Version History                          |    |

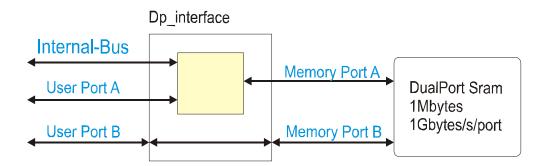

|                  | l Port Memory Interface                  |    |

| 6.18.1           | Functional Description                   |    |

| 6.18.1           | -                                        |    |

| 6.18.1           |                                          |    |

| 6.18.1           |                                          |    |

| 6.18.2           | Instantiation                            |    |

| 6.18.3           | Port Description                         | 96 |

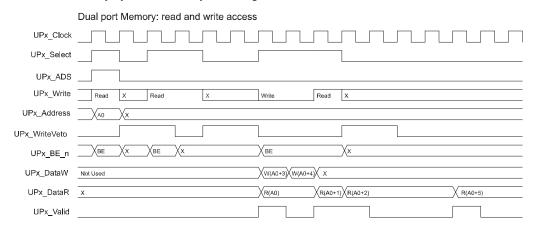

| 6.18.4     | User Port Timing Diagram                                | 98    |

|------------|---------------------------------------------------------|-------|

| 6.18.5     | Registers                                               | 98    |

| 6.18.5.1   | DP_Control                                              | 98    |

| 6.18.5.2   | 2 DP_TestPatternControl                                 | 99    |

| 6.18.5.3   | 3 DP_Status                                             | 99    |

| 6.18.5.4   | DP_TestValue                                            | 99    |

| 6.18.5.5   | 5 DP_TestResult                                         | 99    |

| 6.18.6     | Accessing the Dual Port Memory                          | . 100 |

| 6.18.6.1   | DPMemory                                                | 100   |

|            | Constraints                                             |       |

| 6.18.8     | Resource Utilization                                    | . 100 |

| 6.18.9     | Version History                                         | . 100 |

| 6.19 Dual  | Port Memory Control Example                             | . 101 |

| 6.19.1     | Port Description                                        | . 101 |

| 6.19.2     | Registers                                               | . 102 |

| 6.19.2.1   | Control Register                                        | 102   |

| 6.19.3     | Resource Utilization                                    | . 102 |

| 6.19.4     | Version History                                         | . 102 |

| 6.20 Seria | al Front Panel Data Port Controller                     | . 103 |

| 6.20.1     | Functional Description                                  | . 103 |

|            | Port Description                                        |       |

|            | Detailed Description                                    |       |

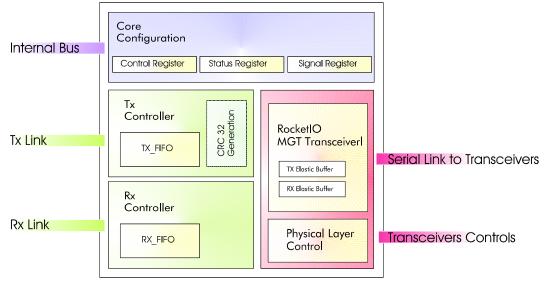

| 6.20.3.1   | TX Controller                                           | 105   |

| 6.20.3.2   |                                                         |       |

| 6.20.3.3   |                                                         |       |

| 6.20.3.4   |                                                         |       |

| 6.20.3.5   | -                                                       |       |

| 6.20.3.6   |                                                         |       |

| 6.20.4     | Register                                                |       |

| 6.20.4.1   | SLC Control Register                                    | 109   |

| 6.20.4.2   | -                                                       |       |

| 6.20.4.3   | -                                                       |       |

| 6.20.5     | Instantiation                                           |       |

| 6.20.6     | Constraints                                             | .112  |

| 6.20.7     | Resource Utilization                                    | .112  |

| 6.20.8     | Version History                                         | .112  |

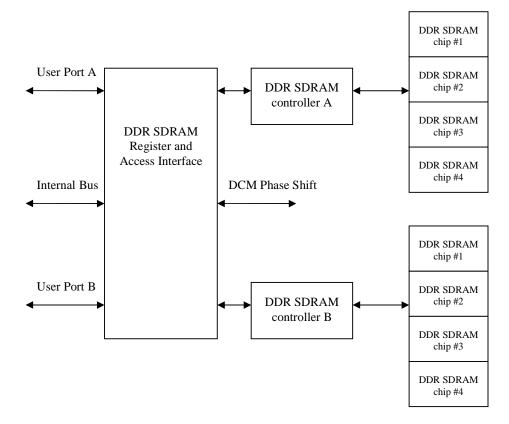

| 6.21 DDF   | Memory Interface                                        | . 113 |

| 6.21.1     | Functional Description                                  | . 113 |

| 6.21.1.1   | Initialization                                          | 113   |

| 6.21.1.2   | 2 Minimum Number of Transfers                           | 114   |

| 6.21.1.3   |                                                         |       |

| 6.21.1.4   | Port Selection                                          | 114   |

| 6.21.1.5   | 5 User Port                                             | 114   |

| 6.21.1.6   | 5 Internal Bus Port                                     | 114   |

| 6.21.1.7   | 7 Internal Bus Port Address versus User Port Address    | 115   |

| 6.21.1.8   | 3 DDR SDRAM Clock Structure                             | 115   |

| 6.21.1.9   | 9 Self-Test                                             | 115   |

| 6.21.2     | Instantiation                                           | . 115 |

| 6.21.3     | Port Description                                        | . 115 |

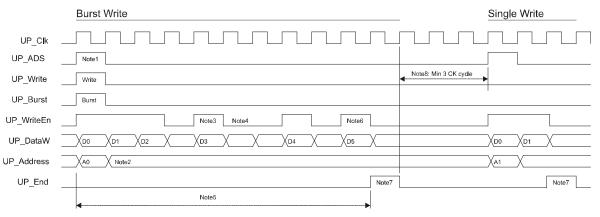

|            | User Port Timing Diagrams: Burst write and Single write |       |

|            | User Port Timing Diagrams: Burst read                   |       |

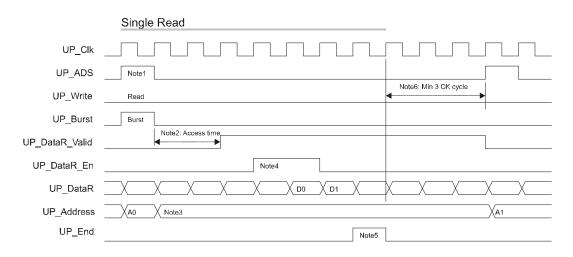

|            | User Port Timing Diagrams: Single Read                  |       |

|            | Registers                                               |       |

| 6.21.7.1   | DDRControl                                              | 118   |

| 6.21.7.2   | 2 DDRStatus                                             | 119   |

| 6.21.7.3   | 3 DDRTestControl                                        | 120   |

| 6.21.7.4   | DDRTestStatus                                           | 120   |

| 6.21.7.5   | 5 DDRTestData0                                          | 121   |

| 6.21.7.                                                                                                                                                       | 6 DDRTestData1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 121                                                                                                                                                                                                                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.21.7.                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                            |

| 6.21.7.                                                                                                                                                       | 8 DDRTestData3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 122                                                                                                                                                                                                                        |

| 6.21.7.                                                                                                                                                       | 9 DDRTestCounter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 122                                                                                                                                                                                                                        |

| 6.21.7.                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                            |

| 6.21.7.                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                            |

| 6.21.8                                                                                                                                                        | Accessing the DDR SDRAM Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 123                                                                                                                                                                                                                        |

| 6.21.8.                                                                                                                                                       | 1 DDR A -memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 123                                                                                                                                                                                                                        |

| 6.21.8.                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                            |

| 6.21.9                                                                                                                                                        | Constraints                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                            |

| 6.21.10                                                                                                                                                       | Resource Utilization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                            |

| 6.21.11                                                                                                                                                       | Version History                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                            |

| 6.22 DD                                                                                                                                                       | R Memory Control Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                            |

| 6.22.1                                                                                                                                                        | Port Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 125                                                                                                                                                                                                                        |

| 6.22.2                                                                                                                                                        | Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 125                                                                                                                                                                                                                        |

| 6.22.2.                                                                                                                                                       | 1 DDREControl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 125                                                                                                                                                                                                                        |

| 6.22.2.                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                            |

| 6.22.3                                                                                                                                                        | Resource Utilization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 126                                                                                                                                                                                                                        |

| 6.22.4                                                                                                                                                        | Version History                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 126                                                                                                                                                                                                                        |

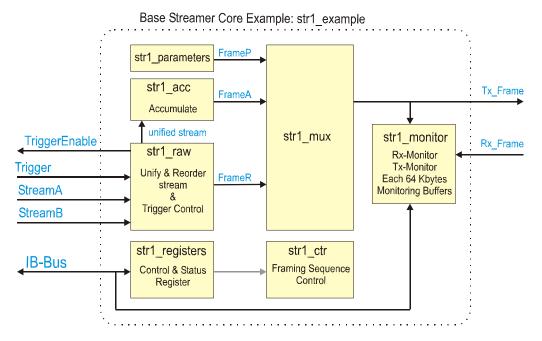

| 6.23 Bas                                                                                                                                                      | e Streamer Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 127                                                                                                                                                                                                                        |

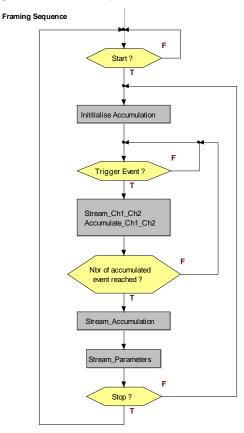

| 6.23.1                                                                                                                                                        | Framing Sequence Flow Chart                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 128                                                                                                                                                                                                                        |

| 6.23.2                                                                                                                                                        | Raw Data Frame                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 128                                                                                                                                                                                                                        |

| 6.23.3                                                                                                                                                        | Accumulated Data Frame                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 128                                                                                                                                                                                                                        |

| 6.23.4                                                                                                                                                        | Parameter Data Frame                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 129                                                                                                                                                                                                                        |

| 6.23.5                                                                                                                                                        | Port Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 129                                                                                                                                                                                                                        |

| 6.23.6                                                                                                                                                        | Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 130                                                                                                                                                                                                                        |

| 6.23.6.                                                                                                                                                       | 1 Main Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 130                                                                                                                                                                                                                        |

| 6.23.6                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                            |

| 6.23.6                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                            |

| 6.23.6                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                            |

| 6.23.7                                                                                                                                                        | Resource Utilization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                            |

| 6.23.8                                                                                                                                                        | Version History                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                            |

| 7. VHDL 1                                                                                                                                                     | TEST BENCH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                            |

|                                                                                                                                                               | rview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                            |

|                                                                                                                                                               | DL Generic of the Tester Component                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                            |

|                                                                                                                                                               | pt Command Syntax                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                            |

|                                                                                                                                                               | A <b>V</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                            |

| 7.3.1                                                                                                                                                         | Lexical Grammar                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                            |

| 7.3.2                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                            |

|                                                                                                                                                               | Syntaxical Grammar                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 135                                                                                                                                                                                                                        |

| 7.3.3                                                                                                                                                         | Syntaxical Grammar<br>Description of the two grammars                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 135<br>135                                                                                                                                                                                                                 |

| 7.3.4                                                                                                                                                         | Syntaxical Grammar<br>Description of the two grammars<br>Special rules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 135<br>135<br>135                                                                                                                                                                                                          |

| 7.3.4<br>7.3.5                                                                                                                                                | Syntaxical Grammar<br>Description of the two grammars<br>Special rules<br>Data files                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 135<br>135<br>135<br>135                                                                                                                                                                                                   |

| 7.3.4<br>7.3.5<br>7.4 Scri                                                                                                                                    | Syntaxical Grammar<br>Description of the two grammars<br>Special rules<br>Data files<br>pt Commands                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 135<br>135<br>135<br>135<br>135<br>136                                                                                                                                                                                     |

| 7.3.4<br>7.3.5<br>7.4 Scri<br>7.4.1                                                                                                                           | Syntaxical Grammar<br>Description of the two grammars<br>Special rules<br>Data files<br>pt Commands<br>Creating Groups: BG / EG                                                                                                                                                                                                                                                                                                                                                                                                                                | 135<br>135<br>135<br>135<br>135<br>136<br>136                                                                                                                                                                              |

| 7.3.4<br>7.3.5<br>7.4 Scri<br>7.4.1<br>7.4.2                                                                                                                  | Syntaxical Grammar<br>Description of the two grammars<br>Special rules<br>Data files<br>pt Commands<br>Creating Groups: BG / EG<br>Displaying Comments: LL                                                                                                                                                                                                                                                                                                                                                                                                     | 135<br>135<br>135<br>135<br>136<br>136<br>136                                                                                                                                                                              |

| 7.3.4<br>7.3.5<br>7.4 Scri<br>7.4.1<br>7.4.2<br>7.4.3                                                                                                         | Syntaxical Grammar<br>Description of the two grammars<br>Special rules<br>Data files<br>pt Commands<br>Creating Groups: BG / EG<br>Displaying Comments: LL<br>Report Control Command                                                                                                                                                                                                                                                                                                                                                                           | 135<br>135<br>135<br>135<br>136<br>136<br>136<br>136                                                                                                                                                                       |

| 7.3.4<br>7.3.5<br>7.4 Scri<br>7.4.1<br>7.4.2<br>7.4.3<br>7.4.3<br>7.4.4                                                                                       | Syntaxical Grammar<br>Description of the two grammars<br>Special rules<br>Data files<br>pt Commands<br>Creating Groups: BG / EG<br>Displaying Comments: LL<br>Report Control Command<br>Defining a Numeric Constant: DC                                                                                                                                                                                                                                                                                                                                        | 135<br>135<br>135<br>136<br>136<br>136<br>136<br>137<br>137                                                                                                                                                                |

| 7.3.4<br>7.3.5<br>7.4 Scri<br>7.4.1<br>7.4.2<br>7.4.3<br>7.4.3<br>7.4.4<br>7.4.5                                                                              | Syntaxical Grammar<br>Description of the two grammars<br>Special rules<br>Data files<br>pt Commands<br>Creating Groups: BG / EG<br>Displaying Comments: LL<br>Report Control Command<br>Defining a Numeric Constant: DC<br>Defining a String Constant: DF                                                                                                                                                                                                                                                                                                      | 135<br>135<br>135<br>136<br>136<br>136<br>137<br>137<br>138                                                                                                                                                                |

| 7.3.4<br>7.3.5<br>7.4 Scri<br>7.4.1<br>7.4.2<br>7.4.3<br>7.4.3<br>7.4.4<br>7.4.5<br>7.4.6                                                                     | Syntaxical Grammar<br>Description of the two grammars<br>Special rules<br>Data files<br>pt Commands<br>Creating Groups: BG / EG<br>Displaying Comments: LL<br>Report Control Command<br>Defining a Numeric Constant: DC<br>Defining a String Constant: DF<br>Executing a Script: EF                                                                                                                                                                                                                                                                            | 135<br>135<br>135<br>136<br>136<br>136<br>136<br>137<br>137<br>138<br>138                                                                                                                                                  |

| 7.3.4<br>7.3.5<br>7.4 Scri<br>7.4.1<br>7.4.2<br>7.4.3<br>7.4.3<br>7.4.4<br>7.4.5<br>7.4.6<br>7.4.7                                                            | Syntaxical Grammar<br>Description of the two grammars<br>Special rules<br>Data files<br>pt Commands<br>Creating Groups: BG / EG<br>Displaying Comments: LL<br>Report Control Command<br>Defining a Numeric Constant: DC<br>Defining a String Constant: DF<br>Executing a Script: EF<br>Run the Simulator: RUN                                                                                                                                                                                                                                                  | 135<br>135<br>135<br>136<br>136<br>136<br>136<br>137<br>137<br>137<br>138<br>138                                                                                                                                           |

| 7.3.4<br>7.3.5<br>7.4 Scri<br>7.4.1<br>7.4.2<br>7.4.3<br>7.4.4<br>7.4.5<br>7.4.6<br>7.4.7<br>7.4.8                                                            | Syntaxical Grammar<br>Description of the two grammars<br>Special rules<br>Data files<br>pt Commands<br>Creating Groups: BG / EG<br>Displaying Comments: LL<br>Report Control Command<br>Defining a Numeric Constant: DC<br>Defining a String Constant: DF<br>Executing a Script: EF<br>Run the Simulator: RUN<br>Writing to Local Bus: CWx                                                                                                                                                                                                                     | <ul> <li>135</li> <li>135</li> <li>135</li> <li>136</li> <li>136</li> <li>136</li> <li>137</li> <li>138</li> <li>138</li> <li>138</li> <li>138</li> <li>139</li> </ul>                                                     |

| 7.3.4<br>7.3.5<br>7.4 Scri<br>7.4.1<br>7.4.2<br>7.4.3<br>7.4.4<br>7.4.5<br>7.4.6<br>7.4.7<br>7.4.8<br>7.4.9                                                   | Syntaxical Grammar<br>Description of the two grammars<br>Special rules<br>Data files<br>pt Commands<br>Creating Groups: BG / EG<br>Displaying Comments: LL<br>Report Control Command<br>Defining a Numeric Constant: DC<br>Defining a String Constant: DF<br>Executing a Script: EF<br>Run the Simulator: RUN<br>Writing to Local Bus: CWx<br>Reading from Local Bus: CRx                                                                                                                                                                                      | <ul> <li>135</li> <li>135</li> <li>135</li> <li>136</li> <li>136</li> <li>136</li> <li>137</li> <li>138</li> <li>138</li> <li>138</li> <li>139</li> <li>140</li> </ul>                                                     |

| 7.3.4<br>7.3.5<br>7.4 Scri<br>7.4.1<br>7.4.2<br>7.4.3<br>7.4.3<br>7.4.4<br>7.4.5<br>7.4.6<br>7.4.7<br>7.4.8<br>7.4.9<br>7.4.10                                | Syntaxical Grammar<br>Description of the two grammars<br>Special rules<br>Data files<br>pt Commands<br>Creating Groups: BG / EG<br>Displaying Comments: LL<br>Report Control Command<br>Defining a Numeric Constant: DC<br>Defining a String Constant: DF<br>Executing a String Constant: DF<br>Executing a String Constant: DF<br>Run the Simulator: RUN<br>Writing to Local Bus: CWx<br>Reading from Local Bus: CRx<br>Writing to Internal Bus: IWx                                                                                                          | <ul> <li>135</li> <li>135</li> <li>135</li> <li>136</li> <li>136</li> <li>136</li> <li>136</li> <li>137</li> <li>138</li> <li>138</li> <li>138</li> <li>139</li> <li>140</li> <li>140</li> <li>140</li> </ul>              |

| 7.3.4<br>7.3.5<br>7.4 Scri<br>7.4.1<br>7.4.2<br>7.4.3<br>7.4.3<br>7.4.4<br>7.4.5<br>7.4.6<br>7.4.7<br>7.4.8<br>7.4.9<br>7.4.10<br>7.4.11                      | Syntaxical Grammar<br>Description of the two grammars<br>Special rules<br>Data files<br>pt Commands<br>Creating Groups: BG / EG<br>Displaying Comments: LL<br>Report Control Command<br>Defining a Numeric Constant: DC<br>Defining a String Constant: DF<br>Executing a String Constant: DF<br>Executing a Script: EF<br>Run the Simulator: RUN<br>Writing to Local Bus: CWx<br>Reading from Local Bus: CRx<br>Writing to Internal Bus: IWx<br>Reading From Internal Bus: IRx                                                                                 | <ul> <li>135</li> <li>135</li> <li>135</li> <li>135</li> <li>136</li> <li>136</li> <li>136</li> <li>136</li> <li>137</li> <li>138</li> <li>138</li> <li>138</li> <li>139</li> <li>140</li> <li>142</li> </ul>              |

| 7.3.4<br>7.3.5<br>7.4 Scri<br>7.4.1<br>7.4.2<br>7.4.3<br>7.4.4<br>7.4.5<br>7.4.6<br>7.4.7<br>7.4.8<br>7.4.9<br>7.4.10<br>7.4.11<br>7.4.12                     | Syntaxical Grammar<br>Description of the two grammars<br>Special rules<br>Data files<br>pt Commands<br>Creating Groups: BG / EG<br>Displaying Comments: LL<br>Report Control Command<br>Defining a Numeric Constant: DC<br>Defining a String Constant: DF<br>Executing a Script: EF<br>Run the Simulator: RUN<br>Writing to Local Bus: CWx<br>Reading from Local Bus: CRx<br>Writing to Internal Bus: IWx<br>Reading From Internal Bus: IRx<br>Clock Generation: CKx                                                                                           | <ul> <li>135</li> <li>135</li> <li>135</li> <li>136</li> <li>136</li> <li>136</li> <li>137</li> <li>138</li> <li>138</li> <li>138</li> <li>139</li> <li>140</li> <li>140</li> <li>142</li> <li>143</li> </ul>              |

| 7.3.4<br>7.3.5<br>7.4 Scri<br>7.4.1<br>7.4.2<br>7.4.3<br>7.4.4<br>7.4.5<br>7.4.6<br>7.4.7<br>7.4.8<br>7.4.9<br>7.4.10<br>7.4.10<br>7.4.11<br>7.4.12<br>7.4.13 | Syntaxical Grammar<br>Description of the two grammars<br>Special rules<br>Data files<br>pt Commands<br>Creating Groups: BG / EG<br>Displaying Comments: LL<br>Report Control Command<br>Defining a Numeric Constant: DC<br>Defining a String Constant: DF<br>Executing a Script: EF<br>Run the Simulator: RUN<br>Writing to Local Bus: CWx<br>Reading from Local Bus: CRx<br>Writing to Internal Bus: IWx<br>Reading From Internal Bus: IRx<br>Clock Generation: CKx<br>Probe Interface: WP                                                                    | <ul> <li>135</li> <li>135</li> <li>135</li> <li>136</li> <li>136</li> <li>136</li> <li>137</li> <li>138</li> <li>138</li> <li>138</li> <li>139</li> <li>140</li> <li>140</li> <li>142</li> <li>143</li> <li>143</li> </ul> |